集成電路測試及測試性設(shè)計(jì)概述

集成電路(Integrated Circuit, IC)是現(xiàn)代電子系統(tǒng)的核心,其功能復(fù)雜性和集成度不斷提升,使得測試成為保證芯片質(zhì)量和可靠性的必要環(huán)節(jié)。集成電路測試是指在芯片制造后或使用過程中,通過施加特定激勵(lì)信號并檢測輸出響應(yīng),以驗(yàn)證其功能、性能和可靠性的過程。測試不僅包括功能測試,還涵蓋參數(shù)測試(如電壓、電流、頻率等)、可靠性測試(如老化測試、環(huán)境適應(yīng)性測試)以及失效分析。有效的測試策略能夠及早發(fā)現(xiàn)制造缺陷、設(shè)計(jì)錯(cuò)誤或潛在故障,從而降低產(chǎn)品返修率、提升客戶滿意度。

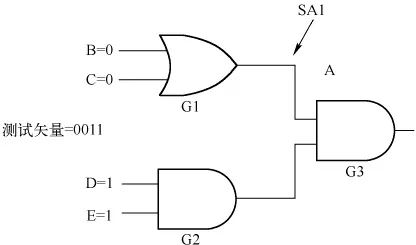

在集成電路設(shè)計(jì)中,測試性設(shè)計(jì)(Design for Testability, DFT)是確保芯片可測試性的關(guān)鍵方法。DFT通過在芯片設(shè)計(jì)階段嵌入專門的測試結(jié)構(gòu)和機(jī)制,以簡化后續(xù)測試過程、降低測試成本和時(shí)間。常見的DFT技術(shù)包括掃描測試(Scan Test)、內(nèi)建自測試(Built-In Self-Test, BIST)和邊界掃描(Boundary Scan)。掃描測試通過將芯片中的觸發(fā)器連接成掃描鏈,使測試人員能夠控制內(nèi)部狀態(tài)并觀察輸出;BIST則利用芯片內(nèi)部電路生成測試模式并分析結(jié)果,減少對外部測試設(shè)備的依賴;邊界掃描則主要用于測試芯片間互連和板級系統(tǒng)。

測試與測試性設(shè)計(jì)在集成電路生命周期中相輔相成。一方面,測試為DFT提供了實(shí)際應(yīng)用場景,推動(dòng)設(shè)計(jì)方法的優(yōu)化;另一方面,DFT通過提高測試覆蓋率、減少測試時(shí)間,提升了整體生產(chǎn)效率。隨著工藝進(jìn)步和芯片復(fù)雜度增加,測試面臨的挑戰(zhàn)也日益突出,例如功耗管理、測試數(shù)據(jù)量爆炸以及新型缺陷的檢測。人工智能和機(jī)器學(xué)習(xí)技術(shù)有望應(yīng)用于測試模式生成和故障診斷,進(jìn)一步提升測試的智能化和自動(dòng)化水平。

集成電路測試及測試性設(shè)計(jì)是確保芯片質(zhì)量、可靠性和市場競爭力的重要支柱。設(shè)計(jì)人員需在早期階段就考慮測試需求,結(jié)合DFT技術(shù),構(gòu)建高效的測試流程,從而推動(dòng)集成電路產(chǎn)業(yè)的持續(xù)發(fā)展。

如若轉(zhuǎn)載,請注明出處:http://m.dislists.com/product/31.html

更新時(shí)間:2026-02-19 09:00:46